Multiple factors need to be addressed and tested when building an ESD protection strategy for your products, it’s all about getting balance and testing its efficiency.

Electronic systems and components are becoming ever more sensitive to ESD. Miniaturization of ICs and semiconductor processes, multiple power requirements in confined spaces, increasing data rates, greater integration of features on a single SoC, combined data and power interfaces – all contribute to a higher risk of damage from transient voltages. Each individual factor places different requirements on ESD and surge protection and some applications present a combination of all the factors, making the ESD protection selection even more challenging.

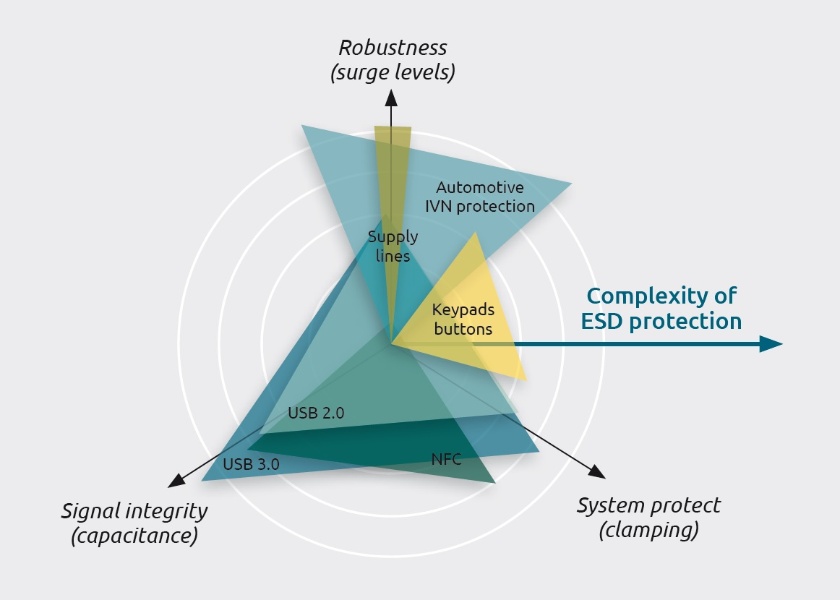

At Nexperia, when we consider what makes an effective ESD protection device we look at three key parameters - which we call the three pillars of ESD protection:

- High robustness - to guard the device against ESD and surge pulses

- Low clamping voltage - to protect SoCs, goes hand-in-hand with low dynamic resistance to ensure clamping voltage doesn't rise if the surge current is increased

- Low capacitance - especially important in high-speed interfaces to maintain excellent signal integrity.

As indicated in the diagram these properties are inter-dependent, so improving one can have a detrimental effect on the others. For some applications, this is not an issue as they only require good performance in one or two properties. However with high rates of data exchanged via interfaces, today’s interconnected world puts an increasing demand for protection devices to deliver optimum performance in all three areas. In these cases, effective solutions must balance all three pillars of ESD protection.

Nexperia’s answer to that is TrEOS protection, which achieves this balance to provide systems with start-of-the-art ESD protection. To ensure solutions are indeed effective against transients and electrostatic discharges, we also go beyond the theory and test our solutions in realistic conditions.

TLP / VF-TLP testing

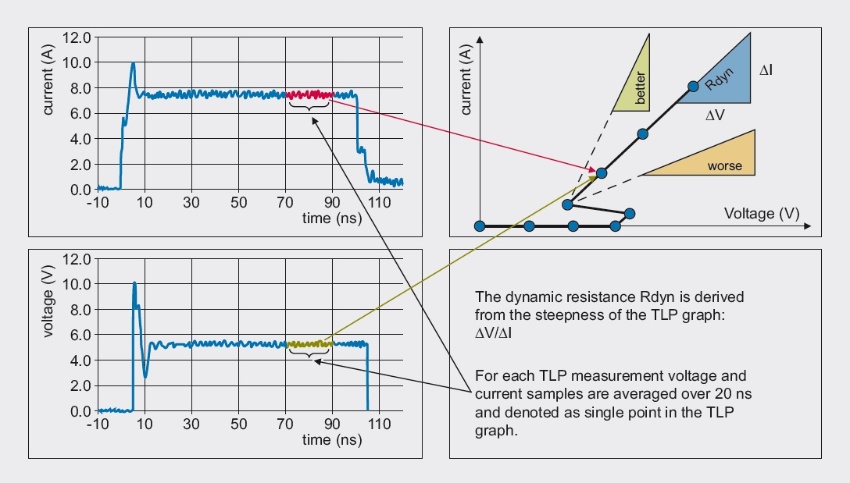

Most electrostatic discharges occur unnoticed by users but can seriously damage sensitive electronics. Standard internationally recognized testing methods and techniques (IEC61000-4-2 / IEC61000-4-5) provide good insight but can vary in results depending on the testing equipment used. As such, with the increasing data rates of today’s high-speed interfaces, two relatively new tests are being used to ensure performance demands are met: TLP (Transmission-Line Pulse) and VF-TLP (Very Fast TLP) testing are widely adopted methods for characterizing complete interfaces and ESD protection components.

TLP measures performance attributes of devices under stresses that have a short pulse width, typically of 100 nanosecond duration, with fast rise and fall times of 1 nanosecond or 600 picoseconds. TLP pulses are roughly equivalent to the energy of a complete ESD pulse. By comparison, VF-TLP uses even shorter test pulses with rise and fall times down to 100 ps. This provides a good indication for determining the switching speed of ESD protection devices and can be extended to check 1st and 2nd peaks separately.

Using the measurement curves produced by the tests helps determine which protection device is suitable to protect a product safely and reliably. In our ESD testing labs, we not only check the performance of our own products but are also performing TLP testing for complete boards. From our experience, this is the best way to find the balance for protecting the entire system as transient voltages can take advantage of any weak point. Our comprehensive real-life testing brings deeper insights and safer outcomes.

Get the balance right for your system

Understanding core parameters and standard testing methods is just a first step in selecting the right ESD protection strategy for your system. Picking an appropriate protection solution also requires understanding of which interfaces needs to be protected and you should consider the whole system’s design and its applications.

For more details, check out our ESD Application Handbook where you will find invaluable information about the causes of electrostatic disturbances, usual failure symptoms and the necessary steps needed to ensure your design incorporates protection that addresses even the most sensitive interface challenges.