USB4™利用USB Type-C®电缆提供的所有发送(Tx)和接收(Rx)线路,可以达到最高40 Gbps的数据速率。这意味着每个差分线对为20 Gbps,相当于每个差分线对的信号基频为10 GHz。虽然以前ESD保护器件的射频性能是通过观察其电容来进行比较的,但这种方法在10 GHz左右已达到了极限。因为ESD保护器件的电容和固有电感能够有效地形成带阻滤波器。

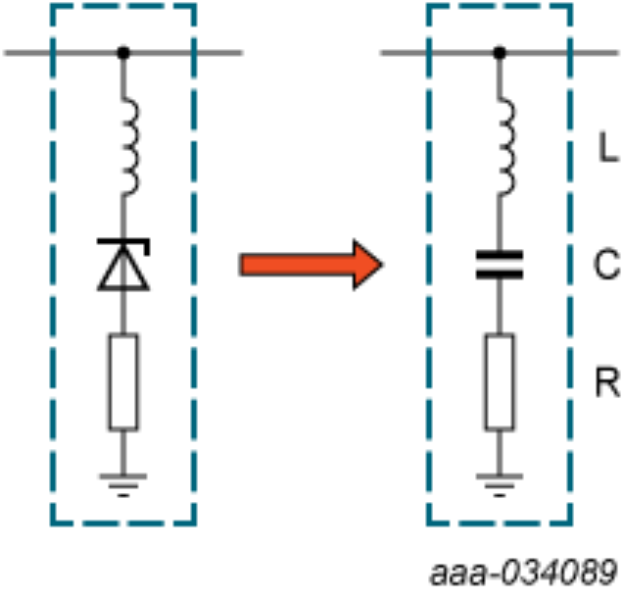

从ESD保护器件的结构来看,其寄生元件可分为电容(主要贡献来自于保护二极管)、电感(主要贡献来自于封装键合线)和电阻。

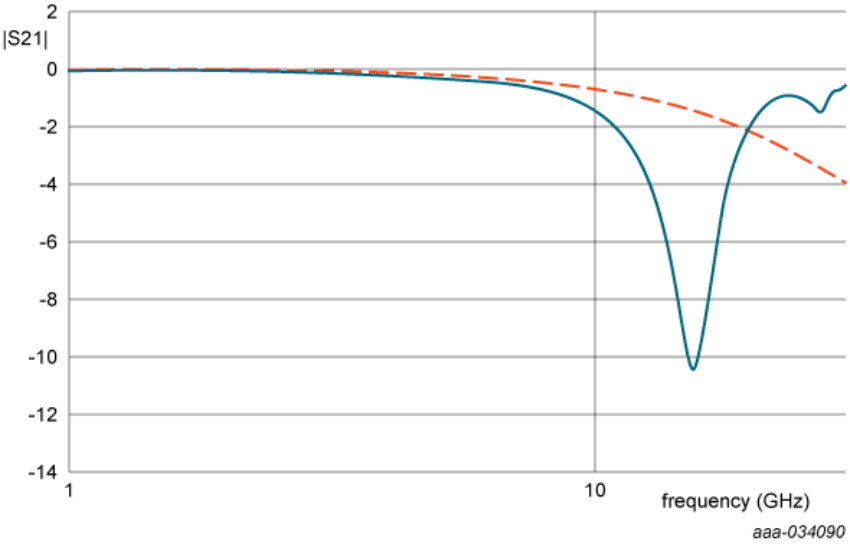

为了强调保护器件电感的重要性,Nexperia比较了测得的焊线ESD保护器件插入损耗行为(实线)与理想电容C(与受测量的器件一样在10 GHz频率下)的计算插入损耗曲线(虚线)。由于焊线电感的原因,10 GHz频率下的偏差比较明显。

显然,电容本身并不能说明器件在10 GHz或更高频率下的行为。我们可清晰地观察到保护器件的带阻谐振频率。在GHz范围内的频率下,应使用散射参数而非电容来评估ESD保护器件的射频适用性。

%20package%20.png)

因此,ESD保护器件针对USB4数据速率的适用性应该通过散射参数来评定,尤其是通过|S21|(插入损耗或αIL)和|S11|(回波损耗或αRL)来描述由于ESD保护器件造成的额外信号衰减和反射。需要注意的是,散射参数是在50欧姆单端系统(100欧姆差分)上测得的,因为这是测量设备的标准,而USB4数据线通常具有90-80欧姆差分(45-40欧姆单端)的线路阻抗。

封装设计如何支持ESD保护的射频性能

因此,与电容相同但电感更高的ESD保护器件相比,电感更低的ESD保护器件具有更出色的射频性能。首先,更低的对地电感使ESD保护器件能够更快速地反应,从而降低ESD脉冲等快速瞬变的钳位。出于这两种原因,高速数据线的ESD保护首选无键合线单片硅封装。窄焊盘封装支持低回波损耗的系统设计。

封装设计如何支持ESD保护的射频性能

关于主机/器件插入损耗预算的概述如下所示。USB4第2代(10 Gbps)的主机/器件预算比USB4第3代(20 Gbps)要小,因此可对长达2m的线缆投入更大预算。

|

|

主机/器件预算 |

频率 |

|

USB3.2 Gen2 (10 Gbps) |

8.5 dB |

5 GHz |

|

USB4 Gen 2 (10 Gbps) |

5.5 dB |

5 GHz |

|

USB4 Gen 3 (20 Gbps) |

7.5 dB |

10 GHz |

虽然选择插入损耗和回波损耗尽可能小的ESD保护器件看似是可取的,且Nexperia可在10 GHz频率下实现低至-0.19 dB的插入损耗和-23.5 dB的回波损耗,但射频性能和钳位性能应实现平衡:就同一技术而言,提高射频性能会降低钳位性能。还会降低ESD保护器件的鲁棒性,但对于高数据速率的收发器IC,我们在实践中发现,在ESD保护器件由于ESD过压而损坏之前,该收发器IC通常已经因为剩余的钳位而损坏。

Nexperia刚刚发布了一款针对高速数据线优化的新产品系列,该系列具有如下射频性能:

|

|

αIL @ 10 GHz, |

αRL @ 10 GHz, |

|

-0.19 |

-23.5 |

|

|

-0.25 |

-19.4 |

|

|

-0.28 |

-19.0 |

相对于交流耦合电容放置ESD保护器件

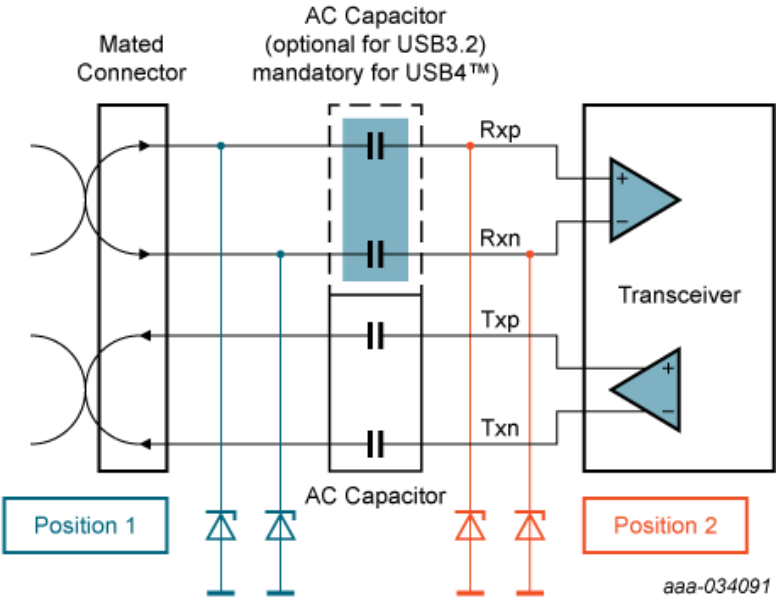

另一个重要的选择是ESD保护器件的位置。USB 3.2在Rx输入之前采用了一个可选交流耦合电容,而该电容则成为USB4™的强制要求。 这样一来,ESD保护器件就只能放置在连接器与连接器正后方的交流耦合电容之间(位置1)或交流耦合电容与收发器之间(位置2)。

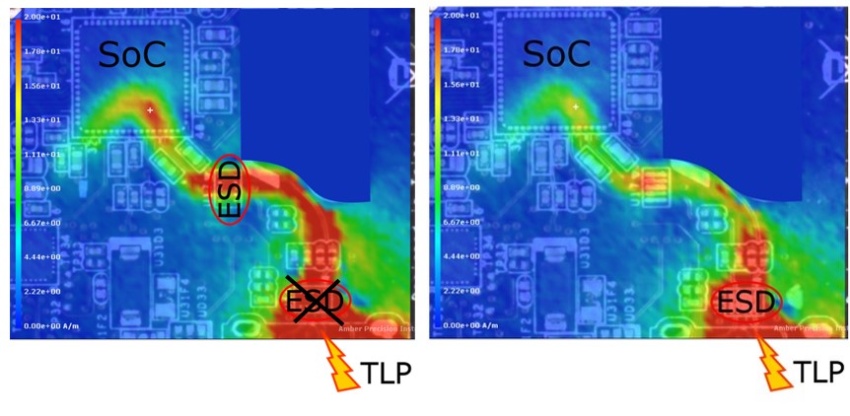

从系统级ESD保护的角度来看,位置1显然是首选位置,原因有两个。首先,在该位置可以对交流耦合电容器提供ESD瞬变保护。其次,为实现最有效的ESD保护,建议在ESD保护器件和收发器IC之间设置尽可能多的线路电感。根据经验,10 mm的附加走线意味着大约3-3.5 nH电感。 为了直观地看到这种效果,我们比较了两个电磁干扰(EMI)扫描仪的测量结果,在此过程中,我们使用了带有两个ESD保护管脚尺寸的USB3板来比较同一ESD保护器件在这两个位置的效率。结果表明,连接器正后方的保护位置可显著降低收发器IC的电场强度。

信号引脚通过TLP脉冲激发,而EMI电场强度则采用二维形式记录。左侧板的ESD保护器件安装在连接器与收发器IC之间的中间位置,而右侧板的ESD保护器件则安装在连接器正后方的首选位置。这降低了系统中的EMI电场强度,尤其是显著降低了收发器IC上的电场强度。

ESD保护器件的位置对保护器件所需的额定电压具有直接影响。USB Type-C®连接器允许连接使用USB3.x标准的器件,而该标准允许的最高电压为2.8 V。如果ESD保护器件在位置1(连接器的正后方),则位置1处使用的ESD保护器件应具有高于2.8 V的VRWM额定电压,正如我们在之前的白皮书中讨论的那样。

综上所述,USB4是提高最常用接口数据传输速度路线图的下一阶段。ESD保护器件能够以较低的插入损耗和回波损耗支持达到这些数据速率。在10 GHz频率范围内,保护器件的低电感开始变得与低电容一样重要。当将保护器件安装在连接器的正后方,以充分利用固有的信号线路电感,保护交流耦合电容时,就可以实现最出色的系统级ESD性能。在这个位置,保护器件的VRWM额定电压需大于2.8 V,因为USB Type-C®允许将USB3.x接口连接至USB4TM接口,而USB3.x接口规格允许的最高电压为2.8 V。